# Microprocessor Reset Circuits With Adjustable Delay Time

## **Description**

The FP6806 asserts a reset signal whenever the  $V_{DD}$  supply voltage declines below the preset threshold and monitors the system voltages from 0.4V to 5V. A time delayed reset can be accomplished with an additional external capacitor. The FP6806 quiescent current is very low and suitable for portable and battery-operated applications.

The output  $\overline{RST}(RST)$  signal is set to be active low.  $\overline{RST}(RST)$  remains low for the delay time after reset condition is deasserted and then goes high. The FP6806 provides  $\pm$  1% threshold accuracy.

FP6806 is available in space-saving TSOT-23-3, TSOT-23-5, TSOT-23-6 packages.

# **Applications**

- Notebook

- TV

- DVD

- Smart Phone

- STB

### **Features**

- Power-On Reset Generator with Adjustable Delay Time: 2ms to 10s (FP6806S9)

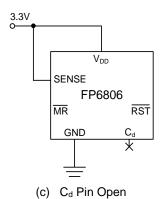

- C<sub>d</sub> Pin Open: RST(RST) Delay 240ms Typical

- C<sub>d</sub> Pin Connected to V<sub>DD</sub> through a Resistor between 100kΩ:  $\overline{RST}(RST)$  Delay 0ms Typical

- Capacitor Adjustable Delay Time

- Very Low Quiescent Current:

1.6µA Typical (FP6806S9)

2.6µA Typical (FP6806S7, FP6806S8)

- High Threshold Accuracy: ± 1% Typical

- Fixed Threshold Voltages for Standard Voltage Rails from 0.8V to 5V (FP6806S9), 1.5V to 5V (FP6806S7, FP6806S8)

- Manual Reset (MR) Input

- Push-Pull RST(RST) Output

- Immune to Short Negative SENSE Voltage

- Guarantee Reset Valid to V<sub>DD</sub>=0.8V

- Available in TSOT-23-3, TSOT-23-5, TSOT-23-6 Packages

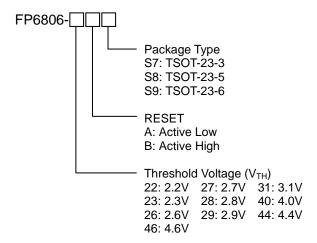

# **Ordering Information**

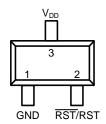

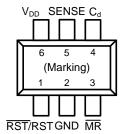

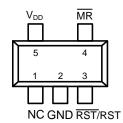

# **Pin Assignments**

S7 Package (TSOT-23-3)

### S9 Package (TSOT-23-6)

### S8 Package (TSOT-23-5)

Figure 1. Pin Assignment of FP6806

### **TSOT-23-3 Marking**

| Part Number  | Product<br>Code | Operation<br>Supply Voltage |

|--------------|-----------------|-----------------------------|

| FP6806-22AS7 | GW1             | 2.2V                        |

| FP6806-23AS7 | GW2             | 2.3V                        |

| FP6806-26AS7 | Gk0             | 2.6V                        |

| FP6806-27AS7 | GW3             | 2.7V                        |

| FP6806-28AS7 | GW4             | 2.8V                        |

| FP6806-29AS7 | Gk1             | 2.9V                        |

| FP6806-31AS7 | GW5             | 3.1V                        |

| FP6806-40AS7 | GW6             | 4.0V                        |

| FP6806-44AS7 | GW7             | 4.4V                        |

| FP6806-46AS7 | GW8             | 4.6V                        |

## TSOT-23-5 Marking

| Part Number     | Product Code | Operation<br>Supply Voltage |

|-----------------|--------------|-----------------------------|

| FP6806-22AS8CTR | GW9          | 2.2V                        |

| FP6806-23AS8CTR | GT0          | 2.3V                        |

| FP6806-26AS8CTR | Gk2          | 2.6V                        |

| FP6806-27AS8CTR | GT3          | 2.7V                        |

| FP6806-28AS8CTR | GX0          | 2.8V                        |

| FP6806-29AS8CTR | Gk3          | 2.9V                        |

| FP6806-31AS8CTR | GX1          | 3.1V                        |

| FP6806-40AS8CTR | GX2          | 4.0V                        |

| FP6806-44AS8CTR | GX3          | 4.4V                        |

| FP6806-46AS8CTR | GX4          | 4.6V                        |

### **TSOT-23-6 Marking**

| Part Number  | Product<br>Code | Operation<br>Supply Voltage |

|--------------|-----------------|-----------------------------|

| FP6806-22AS9 | GX5             | 2.2V                        |

| FP6806-23AS9 | GX6             | 2.3V                        |

| FP6806-26AS9 | GX7             | 2.6V                        |

| FP6806-27AS9 | GX8             | 2.7V                        |

| FP6806-28AS9 | GX9             | 2.8V                        |

| FP6806-29AS9 | GY0             | 2.9V                        |

| FP6806-31AS9 | GY1             | 3.1V                        |

| FP6806-40AS9 | GY2             | 4.0V                        |

| FP6806-44AS9 | GY3             | 4.4V                        |

| FP6806-46AS9 | GY4             | 4.6V                        |

### **TSOT-23-3 Marking**

| Part Number  | Product<br>Code | Operation<br>Supply Voltage |

|--------------|-----------------|-----------------------------|

| FP6806-22BS7 | GY5             | 2.2V                        |

| FP6806-23BS7 | GY6             | 2.3V                        |

| FP6806-26BS7 | GY7             | 2.6V                        |

| FP6806-27BS7 | GY8             | 2.7V                        |

| FP6806-28BS7 | GY9             | 2.8V                        |

| FP6806-29BS7 | GZ0             | 2.9V                        |

| FP6806-31BS7 | GZ1             | 3.1V                        |

| FP6806-40BS7 | GZ2             | 4.0V                        |

| FP6806-44BS7 | GZ3             | 4.4V                        |

| FP6806-46BS7 | GZ4             | 4.6V                        |

## TSOT-23-5 Marking

| Part Number     | Product Code | Operation<br>Supply Voltage |

|-----------------|--------------|-----------------------------|

| FP6806-22BS8CTR | GZ5          | 2.2V                        |

| FP6806-23BS8CTR | GZ6          | 2.3V                        |

| FP6806-26BS8CTR | GZ7          | 2.6V                        |

| FP6806-27BS8CTR | GZ8          | 2.7V                        |

| FP6806-28BS8CTR | GZ9          | 2.8V                        |

| FP6806-29BS8CTR | GT4          | 2.9V                        |

| FP6806-31BS8CTR | GT5          | 3.1V                        |

| FP6806-40BS8CTR | GT6          | 4.0V                        |

| FP6806-44BS8CTR | GT7          | 4.4V                        |

| FP6806-46BS8CTR | GT8          | 4.6V                        |

### **TSOT-23-6 Marking**

| Part Number  | Product<br>Code | Operation<br>Supply Voltage |

|--------------|-----------------|-----------------------------|

| FP6806-22BS9 | GT9             | 2.2V                        |

| FP6806-23BS9 | HA0             | 2.3V                        |

| FP6806-26BS9 | HA1             | 2.6V                        |

| FP6806-27BS9 | HA2             | 2.7V                        |

| FP6806-28BS9 | HA3             | 2.8V                        |

| FP6806-29BS9 | HA4             | 2.9V                        |

| FP6806-31BS9 | HA5             | 3.1V                        |

| FP6806-40BS9 | HA6             | 4.0V                        |

| FP6806-44BS9 | HA7             | 4.4V                        |

| FP6806-46BS9 | HA8             | 4.6V                        |

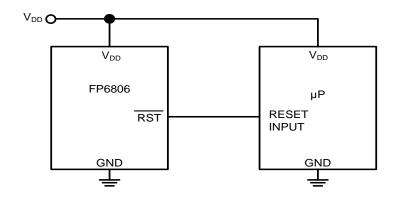

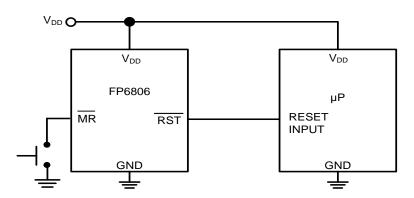

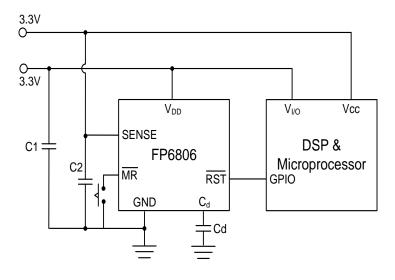

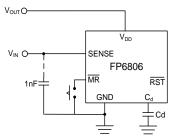

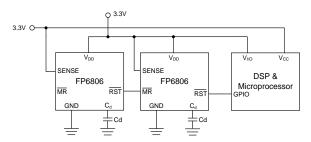

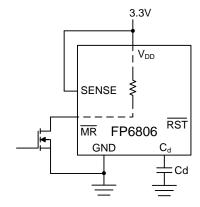

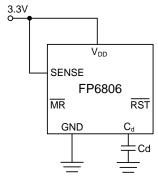

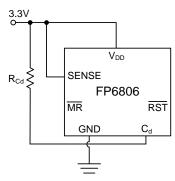

# **Typical Application Circuit**

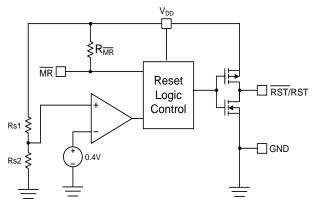

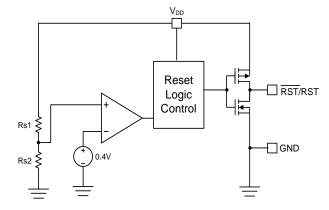

Figure 2. Typical Application Circuit of FP6806S7

Figure 3. Typical Application Circuit of FP6806S8

Figure 4. Typical Application Circuit of FP6806S9

# **Functional Pin Description**

| Pin Name        | Pin No.<br>(TSOT-23-6) | Pin Function                                                                                                                                                        |

|-----------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST/RST         | 1                      |                                                                                                                                                                     |

| GND             | 2                      | Ground.                                                                                                                                                             |

| MR              | 3                      | Manual reset input. Pull $\overline{MR}$ low to manually reset the device. $\overline{MR}$ is internally tied to $V_{DD}$ through a 110k $\Omega$ pull up resistor. |

| C <sub>d</sub>  | 4                      | Reset delay time set pin. Connect a capacitor $\geq$ 150pF between $C_d$ and GND to set the delay time.                                                             |

| SENSE           | 5                      | This pin is connected to the voltage to be monitored. If the voltage at this pin drops below the threshold voltage $V_{TH}$ , $\overline{RST}$ will be asserted.    |

| V <sub>DD</sub> | 6                      | Supply voltage. $V_{DD}$ is the power supply input, and it is recommended to add a $0.1\mu F$ ceramic capacitor close to this pin.                                  |

| Pin<br>Name | Pin No.<br>(TSOT-23-5) | Pin No.<br>(TSOT-23-3) | Pin Function                                                                                                                                                                                                                                                                          |

|-------------|------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC          | 1                      |                        | Non-functional pins.                                                                                                                                                                                                                                                                  |

| GND         | 2                      | 1                      | Ground.                                                                                                                                                                                                                                                                               |

| RST/RST     | 3                      | 2                      | Push-Pull reset output. $\overline{RST}$ remains low for the reset delay time after both SENSE is above $V_{TH}$ and $\overline{MR}$ is set to a logic high. RST remains high for the reset delay time after both SENSE is above $V_{TH}$ and $\overline{MR}$ is set to a logic high. |

| MR          | 4                      |                        | Manual reset input. Pull $\overline{MR}$ low to manually reset the device. $\overline{MR}$ is internally tied to $V_{DD}$ through a 110k $\Omega$ pull up resistor.                                                                                                                   |

| $V_{DD}$    | 5                      | 3                      | Supply voltage. $V_{DD}$ is the power supply input, and it is recommended to add a $0.1\mu F$ ceramic capacitor close to this pin.                                                                                                                                                    |

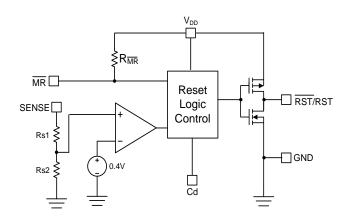

# **Block Diagram**

Figure 5. Fixed Output of FP6806S9

Figure 6. Fixed Output of FP6806S8

Figure 7. Fixed Output of FP6806S7

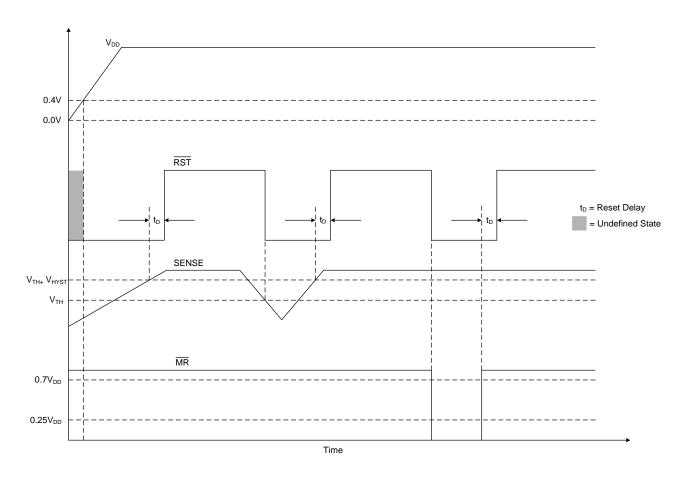

# **Power Timing Chart**

Figure 8. Timing Chart of FP6806AS9

### **Truth Table**

| MR | SENSE > V <sub>TH</sub> | RST/RST |

|----|-------------------------|---------|

| L  | 0                       | L/H     |

| L  | 1                       | L/H     |

| Н  | 0                       | L/H     |

| Н  | 1                       | H/L     |

# Absolute Maximum Ratings (Note1)

| _                                                                                            |                         |

|----------------------------------------------------------------------------------------------|-------------------------|

| • Input Voltage Range, V <sub>DD</sub>                                                       | -0.3V to +6.5V          |

| • C <sub>d</sub> Voltage Range, V <sub>Cd</sub>                                              | -0.3V to $V_{DD}$ +0.3V |

| • Other Voltage Ranges: V <sub>RST</sub> , V <sub>MR</sub> , V <sub>SENSE</sub>              | -0.3V to +6.5V          |

| • RST Pin Current                                                                            | 5mA                     |

| <ul> <li>Power Dissipation @T<sub>A</sub>=25°C (P<sub>D</sub>)</li> </ul>                    |                         |

| TSOT-23-3/5/6                                                                                | 0.4W                    |

| <ul> <li>Package Thermal Resistance (θ<sub>JA</sub>)</li> </ul>                              |                         |

| TSOT-23-3/5/6                                                                                | 250°C/W                 |

| <ul> <li>Package Thermal Resistance (θ<sub>JC</sub>)</li> </ul>                              |                         |

| TSOT-23-3/5/6                                                                                | 110°C/W                 |

| Maximum Junction Temperature (T <sub>J</sub> )                                               | +150°C                  |

| • Storage Temperature Range (T <sub>STG</sub> )                                              | -65°C to +150°C         |

| • Lead Temperature (Soldering, 10sec.)                                                       | +260°C                  |

| Note1: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent dan | nage to the device.     |

| Recommended Operating Conditions                                                             |                         |

| • Supply Voltage, V <sub>DD</sub>                                                            | +1.5V to +6V            |

| • Other Voltage Ranges: V <sub>RST</sub> , V <sub>MR</sub> , V <sub>SENSE</sub>              | -0.3V to +6V            |

| Operation Temperature Range (T <sub>OPR</sub> )                                              | -40°C to +85°C          |

| Operation Junction Temperature Range (T <sub>J</sub> )                                       | -40°C to +125°C         |

|                                                                                              |                         |

# **Electrical Characteristics**

(V<sub>DD</sub>=5V, T<sub>A</sub>=25°C, unless otherwise specified for FP6806S9)

| Parameter                                             | Symbol              | Cond                                                                              | itions                                                                         | Min                | Тур. | Max                 | Unit      |

|-------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------|------|---------------------|-----------|

| Input Supply Range                                    | $V_{DD}$            |                                                                                   | 1.5                                                                            |                    | 6    | V                   |           |

| Supply Current<br>(Current Into V <sub>DD</sub> Pin)  | I <sub>DD</sub>     | $V_{DD}$ =5.5V, $\overline{RST}$ r $\overline{MR}$ , $\overline{RST}$ , $C_d$ Ope | V <sub>DD</sub> =5.5V, RST not Asserted MR. RST. C <sub>d</sub> Open           |                    | 1.6  | 3.3                 | μΑ        |

| Low-Level Output                                      |                     | $1.5V \le V_{DD} < 1.8V$                                                          | , I <sub>OL</sub> =0.4mA                                                       |                    |      | 0.3                 | \ /       |

| Voltage                                               | V <sub>OL</sub>     | 1.8V≦V <sub>DD</sub> <5.5V                                                        | , I <sub>OL</sub> =1.0mA                                                       |                    |      | 0.4                 | V         |

| Power-up Reset Voltage                                |                     | V <sub>OL</sub> (max)=0.2V, I-<br>T <sub>rise(VDD)</sub> ≥15µs/V                  | 1101                                                                           |                    |      | 0.4                 | V         |

| Negative-Going Input<br>Threshold Voltage<br>Accuracy | V <sub>TH</sub>     | Fixed Versions (No                                                                | ote2)                                                                          | -1                 |      | +1                  | %         |

| Hysteresis on $V_{\text{TH}}$ Pin                     | V <sub>HYST</sub>   | Fixed Versions <sup>(Not</sup>                                                    | te2)                                                                           |                    | 1.5  | 3.5                 | $%V_{TH}$ |

| MR Internal Pull up<br>Resistance (Note3)             | $R_{\overline{MR}}$ |                                                                                   |                                                                                | 70                 | 110  |                     | kΩ        |

| Input Current at SENSE<br>Pin                         | I <sub>SENSE</sub>  | Fixed<br>Versions <sup>(Note2)</sup>                                              | V <sub>SENSE</sub> =5.5V                                                       |                    | 1    |                     | μΑ        |

| Input Capacitance,                                    | C <sub>IN</sub>     | C <sub>d</sub> Pin                                                                | $V_{IN}$ =0V to $V_{DD}$                                                       |                    | 30   |                     | pF        |

| Any Pin                                               | CIN                 | Other Pins                                                                        | V <sub>IN</sub> =0V to 5.5V                                                    |                    | 5    |                     | рг        |

| MR Logic Low Input                                    | V <sub>IL</sub>     |                                                                                   | ·                                                                              | 0                  |      | 0.25V <sub>DD</sub> | V         |

| MR Logic High Input                                   | V <sub>IH</sub>     |                                                                                   |                                                                                | 0.7V <sub>DD</sub> |      | $V_{DD}$            | V         |

| Input Pulse width to RST                              | t <sub>w</sub>      | SENSE                                                                             | $V_{IH}$ =1.05 $V_{TH}$ , $V_{IL}$ =0.95 $V_{TH}$                              |                    | 20   |                     | μs        |

|                                                       |                     | C <sub>d</sub> =Open                                                              | See Timing<br>Chart                                                            | 156                | 240  | 324                 | ms        |

| RST Delay Time                                        | +-                  | C <sub>d</sub> =V <sub>DD</sub>                                                   | See Timing<br>Chart                                                            |                    |      | 150                 | μs        |

| KOT Delay Time                                        | t <sub>D</sub>      | C <sub>d</sub> =10nF                                                              | See Timing<br>Chart                                                            | 60                 | 93   | 125                 | ms        |

|                                                       |                     | C <sub>d</sub> =150pF                                                             | See Timing<br>Chart                                                            | 1.07               | 1.65 | 2.22                | ms        |

| Propagation Delay                                     |                     | MR to RST                                                                         | $V_{IH}=0.7V_{DD}$<br>$V_{IL}=0.3V_{DD}$                                       |                    | 150  | 4000                | ns        |

| High-to-Low Level RST Delay                           | t <sub>pHL</sub>    | SENSE to RST                                                                      | V <sub>IH</sub> =1.05V <sub>TH</sub> ,<br>V <sub>IL</sub> =0.95V <sub>TH</sub> |                    | 20   |                     | μs        |

Note2: Refer to "Ordering Information".

Note3: Not production tested.

# **Electrical Characteristics (Continued)**

$(V_{DD}=5V,\,T_A=25^{\circ}C,\,unless$  otherwise specified for FP6806S8)

| Parameter                                            | Symbol           | Col                                                                         | Conditions                                                                     |     | Тур. | Max                 | Unit |

|------------------------------------------------------|------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----|------|---------------------|------|

| Input Supply Range                                   | $V_{DD}$         |                                                                             |                                                                                | 1.5 |      | 6                   | V    |

| Supply Current<br>(Current Into V <sub>DD</sub> Pin) | I <sub>DD</sub>  | $V_{DD}$ =5.5V, $\overline{R}$ : $\overline{MR}$ , $\overline{RST}$ , $C_d$ | ST not Asserted<br>Open                                                        |     | 2.6  | 4.3                 | μΑ   |

| Lavel aval Output Valtage                            |                  | $1.3V \leq V_{DD} <$                                                        | 1.8V, I <sub>OL</sub> =0.4mA                                                   |     |      | 0.3                 |      |

| Low-Level Output Voltage                             | V <sub>OL</sub>  | 1.8V≦V <sub>DD</sub> <                                                      | 5.5V, I <sub>OL</sub> =1.0mA                                                   |     |      | 0.4                 | V    |

| Power-up Reset Voltage                               |                  |                                                                             | $V_{OL}(max)=0.2V, I_{\overline{RST}}=15\mu A, T_{rise(VDD)} \ge 15\mu s/V$    |     |      | 0.4                 | V    |

| Negative-Going Input Threshold Voltage Accuracy      | V <sub>TH</sub>  | Fixed Version                                                               | ns <sup>(Note2)</sup>                                                          | -1  |      | +1                  | %    |

| MR Internal Pull up<br>Resistance (Note3)            | R <sub>MR</sub>  |                                                                             |                                                                                | 70  | 110  |                     | kΩ   |

| MR Logic Low Input                                   | VIL              |                                                                             |                                                                                | 0   |      | 0.25V <sub>DD</sub> | V    |

| MR Logic High Input                                  | V <sub>IH</sub>  |                                                                             |                                                                                |     |      | $V_{DD}$            | V    |

| RST Delay Time                                       | t <sub>D</sub>   |                                                                             |                                                                                | 156 | 240  | 324                 | ms   |

| Propagation Delay                                    |                  | MR to RST                                                                   | $V_{IH}=0.7V_{DD}$<br>$V_{IL}=0.3V_{DD}$                                       |     | 150  | 4000                | ns   |

| High-to-Low Level RST Delay                          | t <sub>pHL</sub> | V <sub>DD</sub> to RST                                                      | V <sub>IH</sub> =1.05V <sub>TH</sub> ,<br>V <sub>IL</sub> =0.95V <sub>TH</sub> |     | 20   |                     | μs   |

## ( $V_{DD}$ =5V, $T_A$ =25°C, unless otherwise specified for FP6806S7)

| Parameter                                            | Symbol          | Conditions                                                                                 | Min | Тур. | Max | Unit |

|------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------|-----|------|-----|------|

| Input Supply Range                                   | $V_{DD}$        |                                                                                            | 1.5 |      | 6   | V    |

| Supply Current<br>(Current Into V <sub>DD</sub> Pin) | I <sub>DD</sub> | V <sub>DD</sub> =5.5V, RST not Asserted                                                    |     | 2.6  | 4.3 | μA   |

| Lave Lavel Output Valtage                            | V <sub>OL</sub> | $1.3V \le V_{DD} < 1.8V$ , $I_{OL} = 0.4mA$                                                |     | 0.3  | V   |      |

| Low-Level Output Voltage                             |                 | $1.8V \le V_{DD} < 5.5V$ , $I_{OL} = 1.0mA$                                                |     |      | 0.4 | V    |

| Power-up Reset Voltage                               |                 | $V_{OL}(max)$ =0.2V, $I_{\overline{RST}}$ =15 $\mu$ A, $T_{rise(VDD)}$ $\geq$ 15 $\mu$ s/V |     |      | 0.4 | V    |

| Negative-Going Input Threshold Voltage Accuracy      | V <sub>TH</sub> | Fixed Versions (Note2)                                                                     | -1  |      | +1  | %    |

| High-to-Low Level RST Delay                          |                 | $V_{DD}$ to $\overline{RST}$ $V_{IH}=1.05V_{TH}$ , $V_{IL}=0.95V_{TH}$                     |     | 20   |     | μs   |

| RST Delay Time                                       | t <sub>D</sub>  |                                                                                            | 156 | 240  | 324 | ms   |

## **Application Information**

The FP6806 are supervisory circuits, which monitors critical voltages and asserts reset signal to the subsequent devices. The FP6806 will assert a  $\overline{RST}$  (RST) signal when either the SENSE (FP6806S9) pin voltage drops below  $V_{TH}$  or the  $\overline{MR}$ (FP6806S8, FP6806S9) pin is driven low. The FP6806 (FP6806S7, FP6806S8, FP6806S9) family can be set to a fixed voltage from 0.8V to 5V, and while the FP6806 (FP6806S9) can set to any voltage above 0.4V by using an external resistor divider.

Once SENSE (FP6806S9) pin exceeds the threshold voltage ( $V_{TH}$ ), an internal timer will keep  $\overline{RST}(RST)$  low(high) for the reset timeout. After this period,  $\overline{RST}(RST)$  will go high(low). If SENSE (FP6806S9) pin falls below the threshold voltage ( $V_{TH}$ ),  $\overline{RST}(RST)$  will go low(high) immediately. The user can select any reset delay time from 2ms to 10s by connecting a capacitor between  $C_d$  and GND (FP6806S9).

The FP6806 (FP6806S7, FP6806S8) family  $\overline{RST}(RST)$  signal is guaranteed to be a logic low (high) for  $V_{TH} > V_{DD} > 0.8V$ . Once  $V_{DD}$  (FP6806S7, FP6806S8) pin exceeds the threshold voltage ( $V_{TH}$ ), an internal timer will keep  $\overline{RST}(RST)$  low (high) for the reset timeout. After this period,  $\overline{RST}(RST)$  will go high (low). If  $V_{DD}$  (FP6806S7, FP6806S8) pin falls below the threshold voltage ( $V_{TH}$ ),  $\overline{RST}(RST)$  will go low (high) immediately.

Whenever  $V_{DD}$  (FP6806S7, FP6806S8) pin drops below the threshold voltage ( $V_{TH}$ ), the internal timer resets to zero and  $\overline{RST}$  (RST) goes low (high). The internal timer keeps activated only when  $V_{DD} > V_{TH}$ , and  $\overline{RST}$  (RST) remains low (high) for the reset timeout interval.

### **Reset Output**

The  $\overline{RST}(RST)$  output is undefined for voltage below 0.4V. If SENSE (FP6806S9) pin or V<sub>DD</sub> (FP6806S7, FP6806S8) pin is above its threshold voltage(V<sub>TH</sub>) and the  $\overline{MR}$  (FP6806S8, FP6806S9) pin is logic high, $\overline{RST}(RST)$  will be driven to a logic high(low). If either SENSE (FP6806S9) pin or V<sub>DD</sub> (FP6806S7, FP6806S8) pin falls below V<sub>TH</sub> or  $\overline{MR}$  (FP6806S8, FP6806S9) pin is driven low,  $\overline{RST}(RST)$  will be asserted. On  $\overline{MR}(FP6806S8, FP6806S9)$  pin is logic high

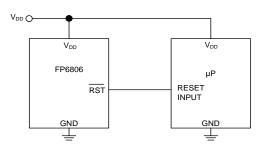

again and SENSE (FP6806S9) pin or  $V_{DD}$  (FP6806S7, FP6806S8) pin is above  $V_{TH}$ , RST(RST) will hold logic low(high) for a specific reset delay time. Once the reset delay time expires, RST (RST) will drive logic high(low). Since the reset output of FP6806 is Push-Pull, Connecting the FP6806's RESET output directly to the microcontroller's RESET pin allows either device to assert reset (Figure 9).

Figure 9. Interfacing to µPs with Bidirectional Reset I/O

### **SENSE Input**

Use SENSE to monitor system voltage. If SENSE (FP6806S9) pin drops below  $V_{TH}$ , the  $\overline{RST}(RST)$  will be asserted. A 1nF to 10nF bypass capacitor can be put between SENSE and GND to reduce additional noise immunity of SENSE pin.

Figure 10. Monitor a User-Defined Threshold Voltage

#### **Thermal Consideration**

The power handling capability of the device will be limited by maximum 150°C operation junction temperature. The power dissipated by the device will be estimated by  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . The power dissipation should be lower than the maximum power dissipation listed in "Absolute Maximum Ratings" section.

## **Application Information (Continued)**

### **Manual Reset Input**

Many µP-based products require manual reset capability, allowing the operator or external logic circuitry to initiate a reset. A logic low on MR (FP6806S8, FP6806S9) pin asserts reset. When MR returns high and SENSE (FP6806S9) is above threshold voltage for the reset delay time, RST(RST) will de-asserted. This input has an internal  $110k\Omega$ pull-up resistor, so it can be left open if it is not used. If MR is driven from long cables or if the device is used in a noisy environment, connecting a 0.1µF capacitor from MR to ground provides additional noise immunity. Figure 11 shows how MR can be used to monitor multiple system voltages. If the MR signal does not reach VDD, there will be additional current draw from V<sub>DD</sub> through  $\overline{MR}$  by internal pull-up resistor. To minimize current draw, a logic-level FET can be used as illustrated in Figure 12.

Figure 11. Applying MR to Monitor Multiple System Voltage

Figure 12. Applying an External NMOSFET to Minimize  $I_{DD}$  When  $\overline{MR}$  Signal does not reach  $V_{DD}$

### **Choose the Reset Delay Time**

Figure 13(a). shows that the FP6806 (FP6806S9) sets the  $\overline{RST}$  (RST) delay time by connecting a capacitor between C<sub>d</sub> and GND. And user can define program time between 2ms and 10s.

The capacitor  $C_d$  must be larger than 150pF. A given delay time of the capacitor value can be calculated by using the following equation:

Cd(nF)=[

$$t_D(s)$$

-0.28×10<sup>-3</sup>(s)]× $\frac{75}{0.7}$

(a) Capacitor adjustable delay time

(b) C<sub>d</sub> Pin Connected to V<sub>DD</sub> through a resistor

Figure 13. Applying to Set the  $\overline{RST}(RST)$ Delay Time

Figure 13(b). shows that the FP6806 (FP6806S9) sets the  $\overline{RST}$  (RST)delay time by connecting a resistor with  $50k\Omega$  to  $300k\Omega$  between  $C_d$  and  $V_{DD}$ . And user can set delay time 0ms.And user can program delay time 240ms by open  $C_d$  Pin. The circuit can refer figure 13(c).

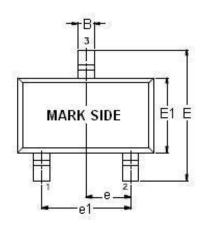

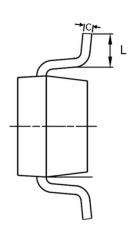

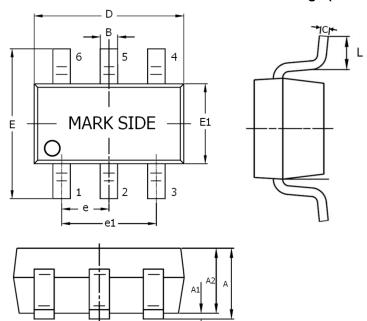

# **Outline Information**

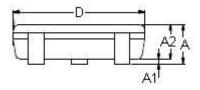

TSOT-23-3 Package (Unit: mm)

| SYMBOLS | DIMENSION IN MILLIMETE |      |  |  |  |

|---------|------------------------|------|--|--|--|

| UNIT    | MIN                    | MAX  |  |  |  |

| Α       | 0.70                   | 0.90 |  |  |  |

| A1      | 0.00                   | 0.10 |  |  |  |

| A2      | 0.70                   | 0.80 |  |  |  |

| В       | 0.30                   | 0.50 |  |  |  |

| D       | 2.80                   | 3.00 |  |  |  |

| Е       | 2.60                   | 3.00 |  |  |  |

| E1      | 1.50                   | 1.70 |  |  |  |

| е       | 0.90                   | 1.00 |  |  |  |

| e1      | 1.80                   | 2.00 |  |  |  |

| С       | 0.08                   | 0.20 |  |  |  |

| L       | 0.30                   | 0.60 |  |  |  |

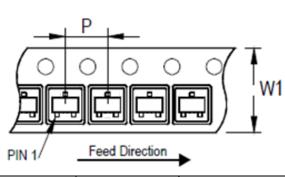

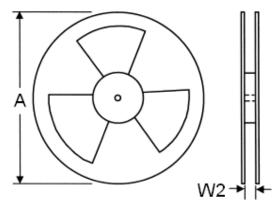

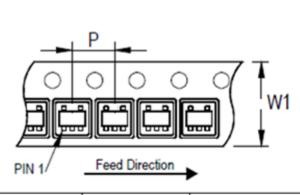

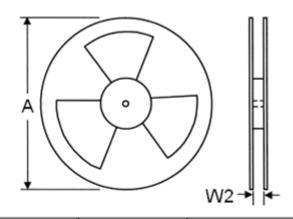

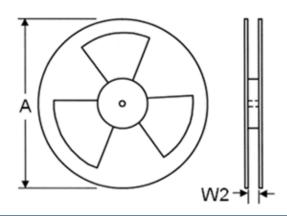

# **Carrier dimensions**

| Tape Size | Pocket Pitch | Reel Size (A) |     | Reel Width | Empty Cavity | Units per Reel |

|-----------|--------------|---------------|-----|------------|--------------|----------------|

| (W1) mm   | (P) mm       | in mm         |     | (W2) mm    | Length mm    |                |

| 8         | 4            | 7             | 180 | 8.4        | 300~1000     | 3,000          |

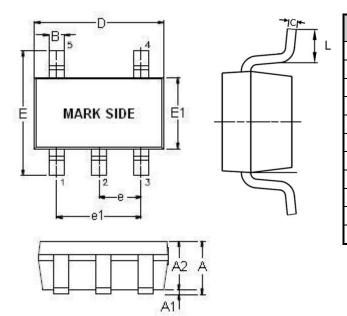

# **Outline Information (Continued)**

TSOT-23-5 Package (Unit: mm)

| SYMBOLS | DIMENSION IN MILLIMETER |      |  |  |  |

|---------|-------------------------|------|--|--|--|

| UNIT    | MIN                     | MAX  |  |  |  |

| Α       | 0.70                    | 0.90 |  |  |  |

| A1      | 0.00                    | 0.10 |  |  |  |

| A2      | 0.70                    | 0.80 |  |  |  |

| В       | 0.30                    | 0.50 |  |  |  |

| D       | 2.80                    | 3.00 |  |  |  |

| Е       | 2.60                    | 3.00 |  |  |  |

| E1      | 1.50                    | 1.70 |  |  |  |

| е       | 0.90                    | 1.00 |  |  |  |

| e1      | 1.80                    | 2.00 |  |  |  |

| С       | 0.08                    | 0.20 |  |  |  |

| L       | 0.30                    | 0.60 |  |  |  |

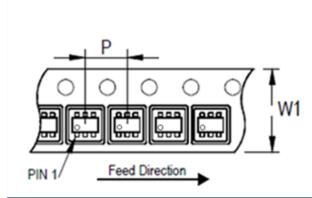

# **Carrier dimensions**

| ١ | Tape Size | Pocket Pitch | Reel Size (A) |     | Reel Width | Empty Cavity | Units per Reel |

|---|-----------|--------------|---------------|-----|------------|--------------|----------------|

|   | (W1) mm   | (P) mm       | in            | mm  | (W2) mm    | Length mm    |                |

|   | 8         | 4            | 7             | 180 | 8.4        | 300~1000     | 3,000          |

# **Outline Information (Continued)**

TSOT-23-6 Package (Unit: mm)

| SYMBOLS | DIMENSION IN MILLIMETER |      |  |  |

|---------|-------------------------|------|--|--|

| UNIT    | MIN                     | MAX  |  |  |

| Α       | 0.70                    | 0.95 |  |  |

| A1      | 0.00                    | 0.10 |  |  |

| A2      | 0.70                    | 0.85 |  |  |

| В       | 0.30                    | 0.50 |  |  |

| D       | 2.80                    | 3.00 |  |  |

| E       | 2.60                    | 3.00 |  |  |

| E1      | 1.50                    | 1.70 |  |  |

| е       | 0.90                    | 1.00 |  |  |

| e1      | 1.80                    | 2.00 |  |  |

| С       | 0.08                    | 0.20 |  |  |

| L       | 0.30                    | 0.60 |  |  |

# **Carrier dimensions**

| Tape Size | Pocket Pitch | Reel Size (A) |     | Reel Width        | Empty Cavity | Units per Reel |

|-----------|--------------|---------------|-----|-------------------|--------------|----------------|

| (W1) mm   | (P) mm       | in            | mm  | (W2) mm Length mm |              |                |

| 8         | 4            | 7             | 180 | 8.4               | 300~1000     | 3,000          |